近年来,关于台积电先进封装的报道越来越多,在这篇文章里,我们基于台积电Douglas Yu早前的一个题为《TSMC packaging technologies for chiplets and 3D》的演讲,给大家提供关于这家晶圆厂巨头在封装方面的的全面解读。为了读者易于理解,在演讲内容的基础上做了部分补充。

本文首先从Douglas Yu演讲目录开始,然后是各项详细的内容。首先,简单地叙述半导体产业迎来了转折点,然后进入本论部分,即TSMC的最先进的封装技术。具体如下,被称为“3D Fabric”的2.5/3D的集成化技术、System scale up和封装内部的互相连接的scale down。

其次,再进入第二项本论一一集成不同类型元件的新封装技术。具体而言,解释最先进的放热技术、硅光电子(Silicon Photonics)的集成化技术。文章的最后为汇总部分。

Front-end 和Back-end的3D封装

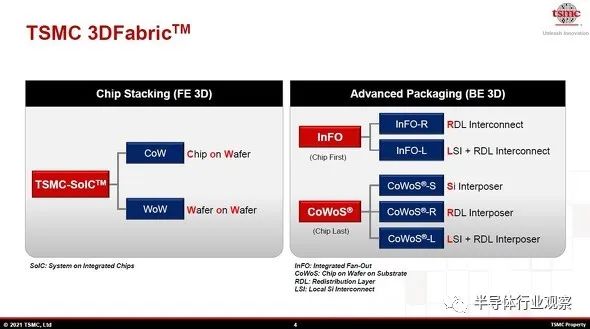

被TSMC称为“3D Fabric”的2.5/3D集成化技术由Front-end(FE 3D) 和Back-end(BE 3D)两处工程构成。Front-end(FE 3D)是一种堆叠硅芯片(Silicon Die)后并相互连接的工艺技术。有多种分类,如将采用不同代际技术生产的硅芯片(Silicon Die)连接起来的技术、把硅芯片(Silicon Die)与其他材质的Die搭载于同一块基板上的技术等。

Back-end(BE 3D)是一种高密度地把多个硅芯片(Silicon Die)连接起来的同时,再与封装基板连接的技术。之前,TSMC开发了用于智能手机的封装技术“InFO(Integrated Fan-Out,集成扇出型)”和用于高性能计算机的封装技术“CoWoS(Chip on Wafer on Substrate,晶圆级封装)”。二者都具有丰富的量产实绩。

TSMC研发的最先进的封装技术一一“3D Fabric”的概要。左边为Front-end(SoIC),右边为Back-end(InFO和CoWoS)。出自TSMC“Hot Chips 33的演讲”。(图片出自:eetimes.jp)

Front-end的SoIC有两种技术,其一为“CoW(Chip on Wafer)”,即一种在硅晶圆(Silicon Wafer)上堆叠芯片(Die)的技术;其二为“WoW(Wafer on Wafer)”,即一种将多片芯片(Silicon Wafer)堆叠起来的技术。此处需要注意的是,SoIC并不是一种将电气信号和电源系统等与外部(封装外部)连接的技术。通过与Back-end的3D Fabric或者传统的封装技术相结合,来实现半导体封装。

就Back-end的“InFO(Integrated Fan-Out,集成扇出型)”而言,它利用线路重布层(RDL:Redistribution Layer,一种将硅芯片(Silicon Die)的输入/输出电极引到外部的排线层)和外部电极(焊锡 Bump)实现高集成度的封装技术(InFO的概要将会在后续文章种进行介绍)。此外,还存在一种被称为“LSI(Local Silicon Interconnect)”的技术,即高密度地连接相邻芯片的技术。

“CoWoS(Chip on Wafer on Substrate,晶圆级封装)”是一种密集地放置硅芯片(Silicon Die)的高集成度封装技术。即在可形成精细的排线和电极的“中间基板(Interpoer)”上密集地放置多个硅芯片(Silicon Die)(CoWoS技术将会在后续文章中详细叙述)。“中间基板(Interpoer)”有硅和RDL两种选择项。

多个裸片(Die)连接技术

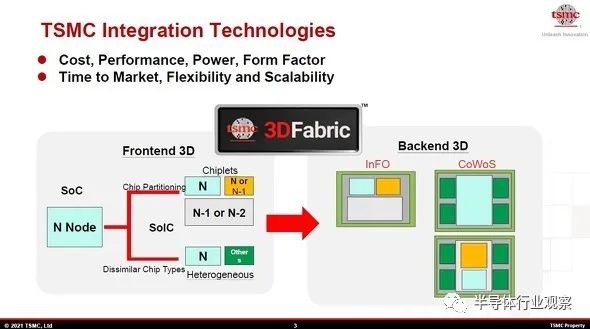

如上文所述,“3D Fabric”由Front-end(FE 3D)和Back-end(BE 3D)两种技术构成。Front-end(FE 3D)中有一种被称为“SoIC(System on Integrated Chips)”的、堆叠连接硅芯片(Silicon Die)的技术,这是一种可以支持“小芯片化”的技术。“小芯片化”指的是有意地将单颗芯片(Single Die)的系统LSI(SoC:System on a Chip)分割为多个芯片(Chiplet)的技术。这项技术最近才开始量产。

Back-end 3D(BE 3D)有两种将多个硅芯片(Silicon Die)高密度相互连接的技术。其一,用于智能手机的“InFO(Integrated Fan-Out,集成扇出型)”;其二,用于高性能计算机(HPC)的“CoWoS(Chip on Wafer on Substrate,晶圆级封装)”。二者都已拥有丰富的量产实绩。

构成“3D Fabric”的Front-end 3D(左侧)和Back-end 3D(右侧)

Front-end 3D的SoIC大致分为两类。其一,利用多个制造代际技术迥异的小芯片(Silicon Die,Mini-die)来完成一个系统(相当于以往的System LSI),即Chiplet结构。可连接的“小芯片(Mini-die)”有各式各样,如利用最先进的工艺技术生产的N代际Mini-die、N-1代际的Mini-die、以及N-2代际的Mini-die等等。

其二,利用工艺技术迥异的多个硅芯片(Silicon Die)组成一个模组(Module),即异构结构(Heterogeneous)。比方说,将利用逻辑半导体工艺生产的硅芯片(Silicon Die)和利用存储半导体工艺技术生产的硅芯片(Silicon Die)组合起来。

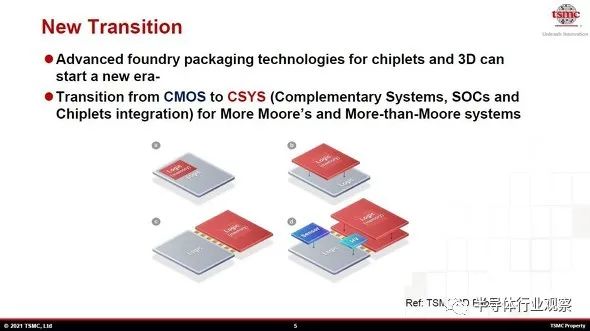

从“CMOS”转为”CSYS”

就以往的半导体研发技术而言,技术每进步一个代际,单个硅芯片(Silicon Die,或者称为Single Chip)上搭载的晶体管数量大约增加两倍。反过来看,每代技术下,集成同样数量的晶体管所需要的硅面积却减少一半。其实现的前提如下,即尽可能地将更多的线路埋入CMOS的单个芯片(Sigle Die)里,即所谓的“单芯片(Monolithic)集成的最大化”。

但是,就当下最先进的7纳米、5纳米代际的CMOS生产而言,将利用不同代际技术生产的多个芯片(Die)组合起来、构成一个系统的做法正在成为最佳解决方案。TSMC把这项解决方案称为“CSYS(Complementary Systems, SoCs and Chiplets integration”。

从CMOS到“CSYS(Complementary Systems, SoCs and Chiplets integration)”

组成一个系统的半导体技术事例。

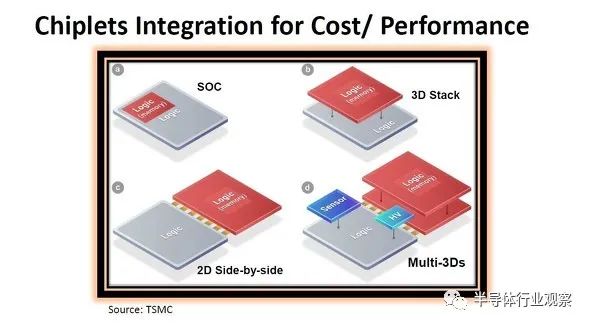

(a)是传统的系统LSI(SoC),在单颗芯片(Sigle Die)上实现最大规模的线路。

(b)为在逻辑芯片(Logic Die)上堆叠逻辑芯片(Logic Die)(或者存储芯片)的事例(SoIC)。

(c)为水平放置逻辑芯片(Logic Die)(或者存储芯片)的事例。

(d)为在(c)的基础上,堆叠传感器芯片(Sensor Die)、高电压线路(HV)、逻辑芯片(Logic Die)(或者存储芯片)的SoIC事例。

以往,人们不会把采用不同工艺生产的硅芯片(Silicon Die)汇集在一起,而是把采用相同工艺技术生产的硅芯片(Silicon Die)封装在一起,且人们认为这有利于降低整体的成本。但是,就7纳米、5纳米等尖端的技术工艺而言,逻辑半导体的微缩化使成本不断增加,同时,难以实现微缩化的线路区块(Block)越来越多。

于是,微缩化的优势仅存在于大型的线路区块(Block)中,而采用尖端工艺变得越来越普遍。相反,将多个芯片(Die)以2.5/3D的形式连接起来的集成技术(即先进封装技术)的比重越来越大。更准确地说,要实现先进系统的研发,先进的封装技术是极其重要的。

用于智能手机的“InFO”的发展

以下开始介绍TSMC研发的先进封装技术的最新发展方向。

TSMC的先进封装技术始于用于高性能计算的“CoWoS(Chip on Wafer on Substrate,晶圆级封装)”和用于智能手机的“InFO(CoWoS(Chip on Wafer on Substrate,集成扇出型)”。“CoWoS”在2012年前后开始被采用,已经有十年的量产实绩。InFO因在2016年被用于“iPhone 7”的“A10”处理器,而被人们熟知。

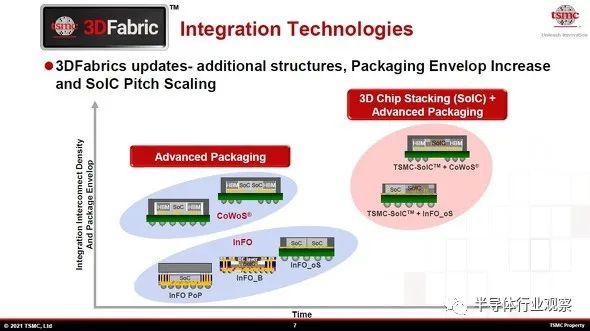

TSMC的最先进的封装技术和其发展。横轴为时间、纵轴为相互连接的密度、封装的大小

CoWoS和InFO已经具有十年以上的研发历史,至此已经派生出多种产品。此外,最近由于SoIC(System on Integrated Chips)研发的进步,将SoIC与CoWoS或者InFO结合的3D封装开始“登场”。

接下来,我们来看看InFO的“衍生品”。就最初的InFO而言,其标准是,在被称为“InFO PoP(Package on Package)”的InFO上搭载低功耗版本的DRAM(封装产品)。主要用途为智能手机的应用处理器(AP)。将AP封装于InFO上,并搭载DRAM,一个小而薄的模组就诞生了。

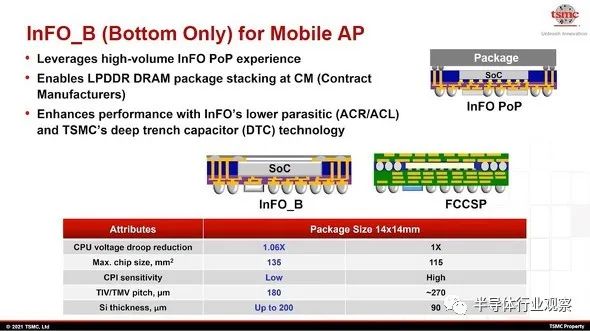

InFO PoP、InFO_B、FCCSP的概图。在下面的表格中比较了InFO_B和FCCSP(二者的外形尺寸都是14mm见方)

最近,又研发了一项名为“InFO_B(Bottom Only)”的技术,即可由TSMC以外的其他企业搭载DRAM。与FCCSP相比,可以获得更高的性能。在外形尺寸同样为14mm见方的情况下,比较InFO_B和FCCSP后发现,InFO_B的优势如下:有效控制电源电压下降、可容纳更大尺寸的芯片(Die)、可容纳更厚的芯片(Die)。

对InFO的另一个重要的研发是,针对高性能计算机(HPC)的改良,这一点我们将在下文中详细叙述。

“InFO”技术在HPC的应用

TSMC研发了用于高性能计算机(HPC)的“CoWoS”,且已有十年以上的量产实绩。CoWoS虽然是一种可应用于高速、高频信号的优秀封装技术,但它有一个致命的弱点。由于“中间基板(Interposer)”采用的是大型的硅基板,因此生产成本极高。

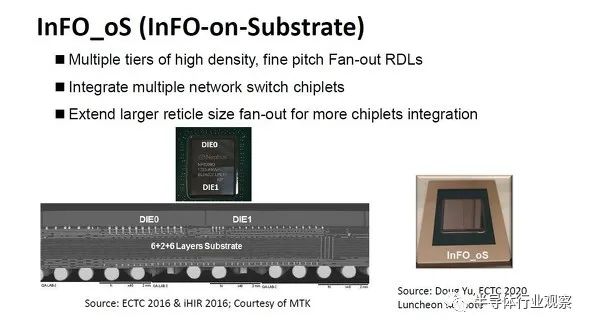

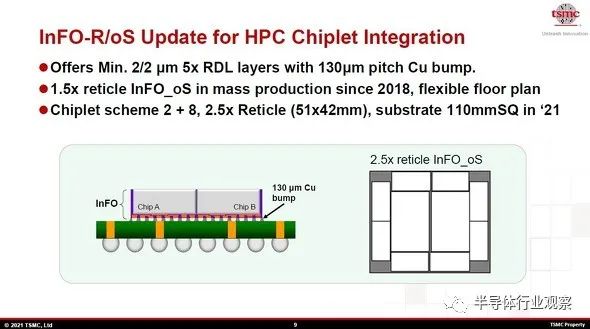

InFO作为一种用于智能手机的封装技术,不需要封装基板。因此,生产成本较低。于是,基于“InFO”,在搭载多个芯片(Multi-die,或者Chiplet)的前提下,通过增加封装基板,试图应用于HPC,即“InFO_oS”,也可以看做是CoWoS的廉价版。

“InFO_oS”的研发事例(可看做是首代产品),左上为从上面看的封装图。将两颗硅芯片(Silicon Die,Chiplet)组合起来的Net-work-switch。左下为断面图。右侧为Net-work-switch的整体图像

“InFO_oS”的概要和结构图,利用RDL(线路重布层, Redistribution Layer)将多个硅芯片(Silicon Die)和基板相连接。RDL的排线的线宽线距极细,为2/2um。RDL的层数为五层。基板和RDL之间通过130um 间距(Pitch)的铜(Cu)凸点(Bump)连接

InFO_oS的首代产品于2018年开始量产。RDL的面积最大可达Reticle的1.5倍(1,287平方毫米左右)。被看做是Net-work-switch模组。第二代产品为搭载了10颗Chiplet的模组。结构如下:两颗逻辑Mini-die,8颗用于输入/输出(IO)的Mini-die。RDL部分的面积为Reticle的2.5倍(51mm×42mm)。基板的大小为110mm见方。预计在2021年内量产第二代产品。

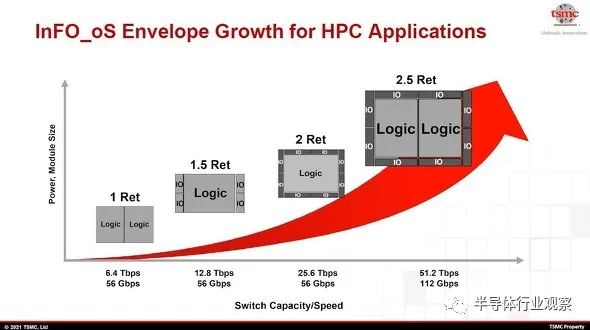

“InFO_oS(用于Net-work-switch的模组)”的研发技术蓝图。横轴为Net-work-switch的性能,纵轴为模组的大小和功耗

介绍两种改良的InFO封装

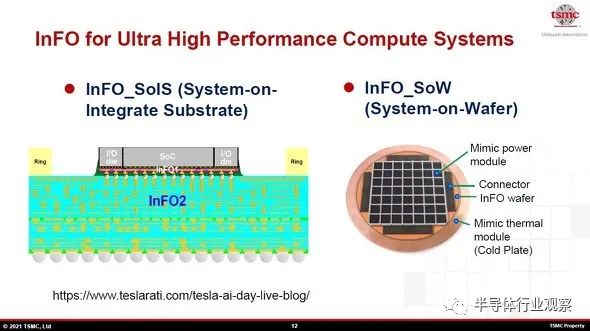

本文开始介绍两种改良了“InFO”技术的封装方式,都是应用于高性能计算机的。其一,堆叠两个“InFO”,即“InFO_SoIS(System on Integrated Substrate)”;其二,在模组(尺寸和晶圆大小相近)上横向排列多个硅芯片(Silicon Die,或者Chip),再通过“InFO”结构,使芯片和输入/输出端子相互连接,即“InFO_SoW(System on Wafer)”。

用于超高性能计算机的“InFO”的改良技术,左侧为支持超高波段(毫米波)的“InFO_SoIS(System on Integrated Substrate)”的断面图,右侧为在大小近似于晶圆的模组上排列多个芯片(Die)的“InFO_SoW(System on Wafer)”的封装事例(概念图)。

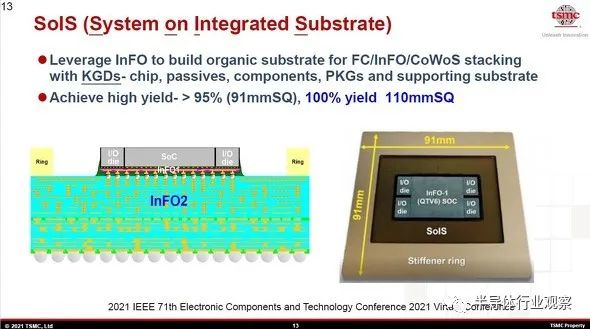

首先,我们介绍一下堆叠了两个“InFO”的“InFO_SoIS(System on Integrated Substrate)”的技术概要。在演讲幻灯片中展示的“InFO_SoIS”封装中展示了如下结构。首先,在RDL(线路重布层,Redistribution Layer)上放置SoC(System on a Chip)芯片和I/O芯片,通过RDL将信号线和电源线引到下面。这种结构被称为“InFO 1”。被引到下面的信号线和电源线经由微型凸块(Micro Bump)与具有多层排线结构的树脂基板(RDL)相连接。在多层树脂基板的底部广泛分布着将信号线和电源线引出的凸块(Bump),且凸块的间距(Pitch)比InFO 1更宽。这种结构被称为“InFO 2”。此外,树脂基板的四周还设计有防止翘曲的“加强环(Stiffener Ring)”。

“InFO_SoIS”的构造图(左)、试做事例(右)。出自TSMC“Hot Chips 33 演讲

试做的“InFO_SoIS”封装品将一个SoC、四个I/O 芯片容纳于InFO 1中,下部由InFO 2支撑。尺寸为91毫米见方。硅芯片(Silicon Die)全部为良品,封装、组装的良率超过95%。此外,100毫米见方的“InFO_SoIS”的封装良率达到了100%。

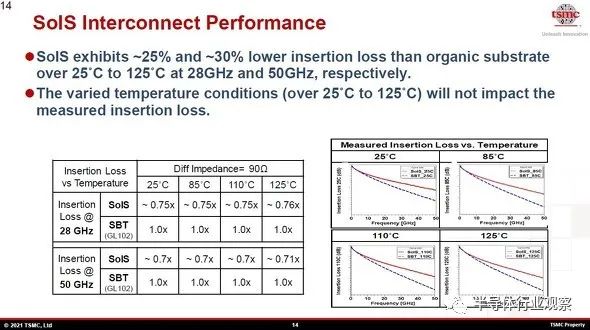

且对试做的“InFO_SoIS”封装品和传统的树脂基板(GL102)在毫米波带中的损耗进行了比较。在28GHz情况下,插入损耗(温度25度一一125度)减少了约25%,在50GHz下,减少了约30%。

“InFO_SoIS”在毫米波带上的插入损失,并与传统的树脂基板(GL102)进行比较。左下的表格为28GHz和50GHz的相对值(把传统基板视为单位“1”),右下方的图表为插入损失的周波特性

InFO实现了晶圆级超大处理器

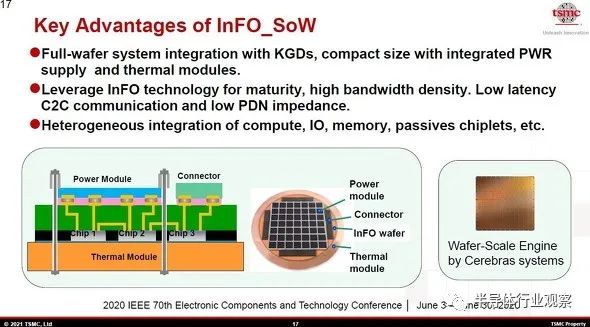

上文中,我们介绍了支持毫米波信号的“InFO_SoIS”的概要,下面我们介绍晶圆级(Wafer Scale)的超大型封装技术一一“InFO_SoW”的概要。“InFO_SoW”技术被AI初创公司Cerebras Systems研发的晶圆级深度学习处理器“WSE(Wafer Scale Engine)”采用。WSE的芯片尺寸极大,为215毫米见方,与直径为300毫米的硅晶圆相匹配。

“InFO_SoW”技术的特点如下,将大规模系统(由大量的硅芯片组成)集成于直径为300毫米左右的圆板状模组(晶圆状的模组)上。通过采用InFO技术,与传统的模组相比较,可以获得更小型、更高密度的系统。

“InFO_SoW”技术的特点(上)、结构(左下)、研发事例(右下)

模组的构成如下:晶圆状的放热模组(Plate)、硅芯片(Silicon Die)群、InFO RDL、电源模组、连接器等。硅芯片群的相互连接、硅芯片群和电源模组以及连接器之间的连接都借由RDL完成。

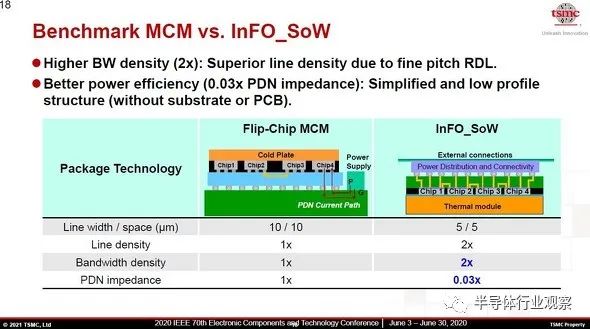

比较利用倒装芯片(Flip Chip)技术的Multi-chip-module(MCM)和“InFO_SoW”

演讲中,还比较了采用倒装芯片(Flip Chip)技术的Multi-chip-module(MCM)和“InFO_SoW”。与MCM相比,相互连接的排线宽度、间隔缩短了二分之一,排线密度提高了两倍。此外,单位面积的数据传输速度也提高了两倍。电源供给网络(PDN)的阻抗(Impedance)明显低于MCM,仅为MCM的3%。

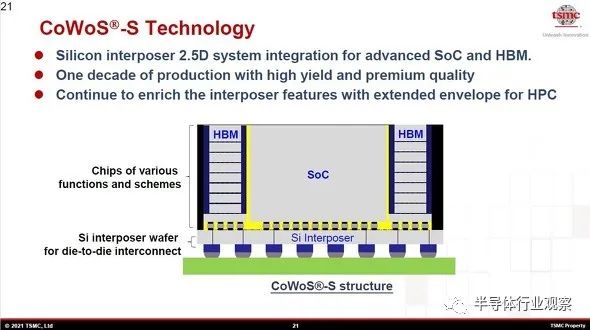

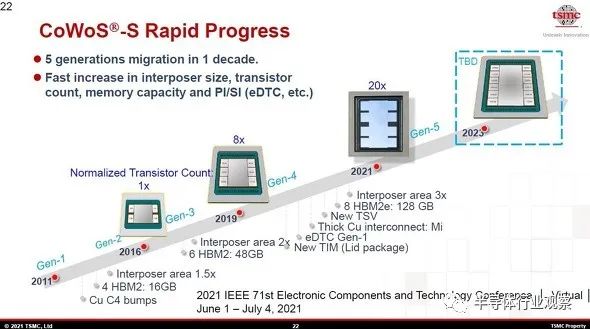

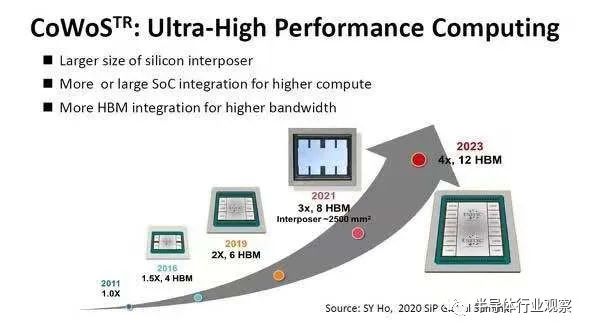

CoWoS:十年五代的封装技术

如上文所述,TSMC根据中间基板(Interpoer)的不同,把“CoWoS”分为三种类型。第一,把硅(Si)基板当做中间基板,即CoWoS_S(Silicon Interposer),这就是在2011年研发的最初的“CoWoS”技术,与过去的“CoWoS”相比,它的先进之处在于,它是一种把硅基板当做中间基板的先进封装技术。

第二为“CoWoS_R(RDL Interposer)”,即把RDL(线路重布层,Redistribution Layer)当做中间基板。第三为“CoWoS_L(Local Silicon Interconnect and RDL Interposer)”,即把小型的硅芯片(Silicon Die)和RDL当做中间基板。但是,需要读者留意的是,TSMC把“Local Silicon Interconnect”缩写为“LSI”。

“CoWoS_S(原来的CoWoS)”的断面结构图。即2.5D封装的代表事例。通过在作为中间基板(Interposer)的硅基板上形成高密度排线、硅通孔(TSV),不仅可以高密度地放置硅芯片(Silicon Die),还可以高速传输信号

“CoWoS_S(原来的CoWoS)”是在2011年开发的,且被称为“第一代(Gen-1)”。被Xilinx的高端FPGA等产品采用。硅制中间基板的最大尺寸为775平方毫米(25mmx31mm)。几乎接近于一张Reticle 的曝光尺寸(26mm×33mm,ArF液浸式扫描情况下)。即,FPGA芯片(Die)的生产技术为28纳米的CMOS工艺。就采用了此款技术的Xilinx的高端FPGA“7V2000T”而言,将四颗FPGA逻辑芯片搭载于“CoWoS_S”上。

就2014年研发的第二代“CoWoS_S”而言,硅制中间基板的尺寸扩大到了1,150平方毫米。接近于1.5张Reticle的曝光面积(1,287平方毫米)。在2015年,被Xilinx的高端FPGA“XCVU440”采用。搭载了三颗FPGA的逻辑芯片。FPGA芯片的制造技术为20纳米的CMOS工艺。

就2016年研发的第三代“CoWoS_S”而言,虽然硅制中间基板的尺寸没有什么变化,但是首次混合搭载了高速DRAM模组(HBM)、逻辑芯片。在2016年,被NVIDIA的高端GPU(GP100)采用。混合搭载了GPU芯片和“HBM2”。“HBM2”为硅芯片(Silicon Die)压层模组(通过TSV将四颗DRAM芯片和一颗Base Die(位于最下层)连接起来),“GP100”上搭载了四颗HBM2模组。将容量为16GB(128GBit)的DRAM和GPU高速连接。

就2019年研发的第四代“CoWoS_S”而言,硅制中间基板的尺寸扩大至相当于两张Reticle的曝光面积。几乎达到了1,700平方毫米。这款大型的中间基板上混合搭载了大规模的逻辑芯片和六个HBM2。单个HBM2的存储容量增加到了8GB(64GBit),因此合为计48GB(384 GBit),容量是第三代的三倍。

“CoWoS_S(原来的CoWoS)”的发展历程。从2011年的第一代到2021年的第五代,一直在改良

如上所述,原本中间基板的尺寸就很大,如今愈来愈大。第一代的面积为775mm2(相当于一张Reticle),第二代和第三代的面积相当于1.5张Reticle,分别为1,150mm2、1,170mm2。第四代面积进一步增大,相当于两张Reticle,为1,700mm2。

最初搭载在中间基板上的硅芯片(Silicon Die)为多个逻辑芯片(Logic Die),第三代以后开始混搭逻辑芯片和存储芯片。即开始混合搭载逻辑芯片(SoC)、高速DRAM模组“HBM(High Bandwidth Memory)”的压层芯片(Die)群。具体而言,一颗SoC芯片和四颗HBM(4Gbit*4颗,合计为16Gbit)。就第四代而言,在SoC芯片面积(集成程度)扩大的同时,混搭的HBM增至六个。通过将单个HBM的存储容量增加两倍,使HBM的总容量较第三代增长了三倍(48Gbit)。

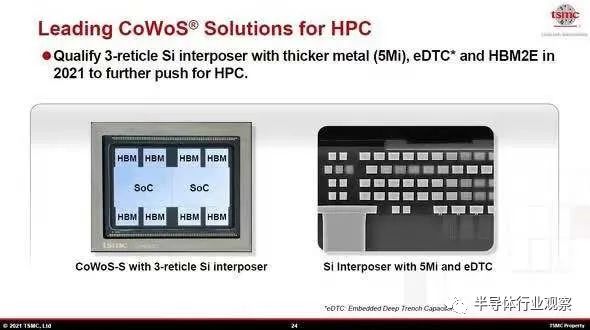

就今年(2021年)第五代(CoWoS_S,原来的CoWoS)而言,硅制中间基板的面积扩大至2,500mm2,相当于三张Reticle,同时,搭载了八个HBM,这相当于第三代的两倍。逻辑硅芯片(Logic Silicon Die)还是Chiplet,两颗Mini-die被放置在1,200mm2的区域内。可搭载的HBM的规格为“HBM2E(即HBM的第二代强化版)”。

就硅制中间基板的RDL(线路重布层,Redistribution Layer)而言,通过提高铜(Cu)排线的厚度,使方块电阻(Sheet Resistance)减少了一半(甚至更多)。通过5层铜排线使硅芯片(Silicon Die)相连接。此外,为了进一步减少硅通孔(Through Silicon Via, TSV)的高频损耗,针对TSV进行了再次设计。在2GHz~14GHz高频带的插入损耗(S21)为0.1dB(甚至更高),重新设计后为0.05dB。此外,通过将“嵌入式深沟电容(eDTC,embedded Deep Trench Capacitor)”装入硅制中间基板,稳定了电源系统。eDTC的容量密度为300nF/mm2。在100MHz~2GHz频带,电源分布网络(PDN)的电阻抗(Impedance)减少了35%(得益于eDTC)。

支持第五代“CoWoS_S(以往的CoWoS)”的技术要素

新一代(第六代)的“CoWoS_S”预计在2023年研发。硅制中间基板的尺寸达到4张Reticle的尺寸。计算下来为3,400mm2左右(约58.6mm见方)。逻辑部分搭载两颗(或者更多)Mini-die,存储部分搭载了12个HBM。对应的HBM的规格为“HBM3”。

“CoWoS_S(以往的CoWoS)”的研发产品路线图(Road Map)

资讯来源:半导体行业观察